That isn't modeling a register, so let's remove that. When you're not reseting the register, and we're not on the rising_edge, you unconditionally set the output to '0'.

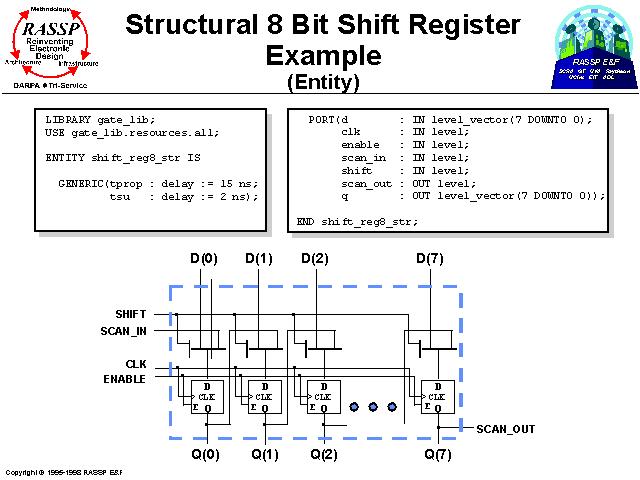

So far I believe to have made a 1-bit register, here is my code: LIBRARY ieee ĭ : IN STD_LOGIC_VECTOR(31 DOWNTO 0) - input.ĪRCHITECTURE description OF register32 ISĮlsif d = '1' and ld = 1 and clk'event and clk='1' thenĮlsif d = '0' and ld = 1 and clk'event and clk='1' then Main inputs of the register include clock (clk), clear (clr), load/enable(ld) signals and an n-bit data (d). I'm having some troubles in designing a 1-bit and 32-bit register in VHDL.

0 kommentar(er)

0 kommentar(er)